Настоящей статьей мы открываем новый цикл исследований, посвященных модулям оперативной памяти типа DDR3. Говорить о наступлении «эпохи DDR3», на наш взгляд, немного преждевременно. Поскольку процессоры новой архитектуры AMD «K10» семейства Phenom X4 (несомненным преимуществом которых является наличие интегрированного контроллера памяти), способные поддерживать память DDR3, еще даже не анонсированы, единственной платформой на сегодняшний день, способной функционировать с модулями памяти DDR3, является платформа Intel на базе двух- или четырехъядерных процессоров семейства Intel Core 2 и чипсетов Intel 3 Series с «официальной» тактовой частотой системной шины 333-400 МГц. Эта платформа способна обеспечить производительность подсистемы памяти на уровне не выше двухканальной DDR2-800, что делает несколько излишним и неоправданным применение более скоростных вариантов вроде DDR2-1066 и, в особенности, еще более скоростной памяти DDR3. Но практика показывает, что реальность способна преподносить интересные сюрпризы, позволяющие пересмотреть столь категоричное отношение, следующее из теории. Именно это мы и сделаем в настоящей статье.Информация о производителе модуля

Производитель модуля: Corsair Memory

Производитель микросхем модуля: неизвестен

Сайт производителя модуля: www.corsair.com/products/dominator.aspxВнешний вид модулей

Рассматриваемые модули внешне похожи на исследованные ранее модули памяти серии DOMINATOR типа DDR2 — TWIN2X2048-10000C5DF, TWIN2X2048-9136C5D и TWIN2X2048-8888C4D (естественно, за исключением внешнего вида контактов и расположения ключа). Напомним, что особенности дизайна продуктов серии DOMINATOR связаны с применением новой технологии охлаждения, именуемой Dual-path Heat Xchange (DHX(tm)), суть которой заключается в организации теплоотвода двумя путями — через выводы микросхем BGA на печатную плату (PCB) модуля, а также с корпуса микросхем BGA на высокоэффективные радиаторы из экструдированного алюминия.

Модули серии DOMINATOR могут также дополнительно охлаждаться специальной системой охлаждения DOMINATOR Airflow Fans, создающей прямой воздушный поток на модули памяти для улучшенного рассеивания тепла и активного отвода его от модулей памяти. Данная система охлаждения входит в комплект поставки рассматриваемых модулей памяти TWIN3X2048-1800C7DFIN G.Part Number модуля

Руководство по расшифровке Part Number модулей памяти DDR3 серии DOMINATOR на сайте производителя отсутствует.

В брошюре модулей TWIN3X2048-1800С7DFIN G указывается, что продукт представляет собой комплект из двух модулей CM3X1024-1800С7DIN объемом 1 ГБ каждый. Модули поддерживают расширение DDR3 SPD — стандарт Intel Extreme Memory Profiles (XMP), позволяющий энтузиастам, геймерам и оверклокерам автоматически получить максимум производительности подсистемы памяти на материнских платах платформы Intel, обладающих поддержкой этого стандарта. Производитель на 100% гарантирует функционирование модулей на материнских платах Intel Extreme Series, поддерживающих память DDR3, в неофициальном режиме DDR3-1800 при таймингах профиля XMP 7-7-7-20 и питающем напряжении 2.0 В. В то же время, в стандартной части SPD в качестве режима по умолчанию указан довольно консервативный стандартный режим DDR3-1333 с таймингами 9-9-9-24.Данные микросхемы SPD модулей

Описание общего стандарта SPD:

JEDEC Standard No. 21-C, 4.1.2 - SERIAL PRESENCE DETECT STANDARD, General Standard

Описание специфического стандарта SPD для DDR3:

Открытое описание специфического стандарта SPD для DDR3 на сайте JEDEC в настоящее время недоступно. Расшифровка содержимого SPD рассматриваемых модулей была произведена в соответствии с предварительной версией стандарта DDR3 SPD 1.0, любезно предоставленной нам компанией Corsair Memory.

| Параметр | Байт(ы) | Значение | Расшифровка |

|---|---|---|---|

| Количество байт SPD (количество используемых байт, полное количество байт SPD, область вычисления CRC) | 0 | 92h | Используемых байт: 176 Всего байт: 256 CRC: байты 0-116 |

| Номер ревизии SPD | 1 | 10h | Ревизия 1.0 |

| Тип устройства DRAM | 2 | 0Bh | DDR3 SDRAM |

| Емкость микросхемы и количество логических банков | 4 | 02h | Емкость: 1 Гбит Кол-во банков: 8 |

| Адресация SDRAM: количество адресных линий строки и столбца микросхемы | 5 | 11h | Кол-во столбцов: 10 Кол-во строк: 13 |

| Организация модуля: ширина внутренней шины данных микросхем модуля, количество физических банков (ранков) | 7 | 01h | Ширина устройства: 8 бит Кол-во ранков: 1 |

| Ширина внешней шины данных модуля (включая ECC) | 8 | 03h | Ширина модуля: 64 бит Расширение ECC: нет |

| Точный опорный временной интервал (FTB) (делимое : делитель) | 9 | 51h | 5 пс (5:1) |

| Основной опорный временной интервал (MTB) (делимое : делитель) | 10, 11 | 01h, 08h | 0.125 нс (1:8) |

| Минимальный временной цикл (tCKmin) | 12 | 0Ch | 1.5 нс (DDR3-1667) |

| Поддерживаемые длительности сигнала CAS# (CL) | 14, 15 | 34h, 00h | Бит 2: CL = 6 Бит 4: CL = 8 Бит 5: CL = 9 |

Минимальная задержка CAS# (tAAmin) | 16 | 6Ch | 13.5 нс (9 тактов) |

| Минимальный период восстановления после записи (tWRmin) | 17 | 78h | 15.0 нс (10 тактов) |

| Минимальная задержка между RAS# и CAS# (tRCDmin) | 18 | 6Ch | 13.5 нс (9 тактов) |

| Минимальная задержка между активизацией соседних строк (tRRDmin) | 19 | 30h | 6.0 нс (4 такта) |

| Минимальное время подзарядки данных в строке (tRPmin) | 20 | 6Ch | 13.5 нс (9 тактов) |

| Минимальная длительность импульса сигнала RAS# (tRASmin) | 22, 21 | 20h, 11h | 36.0 нс (24 такта) |

| Минимальное время цикла строки (tRCmin) | 23, 21 | 8Ch, 11h | 49.5 нс (33 такта) |

| Минимальное время цикла регенерации (tRFCmin) | 24, 25 | D0h, 02h | 90.0 нс (60 тактов) |

| Минимальная внутренняя задержка между командами WRITE и READ (tWTRmin) | 26 | 3Ch | 7.5 нс (5 тактов) |

| Минимальная внутренняя задержка между командами READ и PRECHARGE (tRTPmin) | 27 | 3Ch | 7.5 нс (5 тактов) |

| Минимальное время задержки Four Activate Window (tFAWmin) | 29, 28 | F0h, 00h | 30.0 нс (20 тактов) |

| Дополнительные возможности SDRAM | 30 | 83h | Бит 0: поддержка RZQ/6 Бит 1: поддержка RZQ/7 Бит 7: поддержка DLL-Off |

| Температурный режим и режим регенерации SDRAM | 31 | 05h | Бит 0: расширенный диапазон температур (0-95°C) Бит 2: автоматическая саморегенерация (ASR) |

| Идентификационный код производителя модуля | 117, 118 | 02h, 9Eh | Corsair Memory |

| Дата изготовления модуля | 120-121 | 00h, 00h | Не указана |

| Серийный номер модуля | 122-125 | 00h, 00h, 00h, 00h | Не указан |

| Контрольная сумма | 126-127 | 1Dh, 98h | 981Dh (верно) |

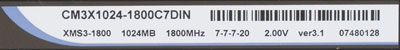

| Part Number модуля | 128-145 | — | CM3X1024-1800C7DHX |

| Идентификационный код производителя микросхем | 148, 149 | 00h, 00h | Не указан |

Способ представления информации в SPD модулей памяти DDR3 претерпел довольно существенные изменения. Прежде всего, несколько по-иному кодируются физические характеристики модуля памяти и его микросхем. Так, для последних указывается полная емкость массива (количество бит), количество логических банков и ширина (разрядность) внутренней шины данных (в битах). Для получения привычного вида конфигуркции микросхемы памяти полную емкость массива (в нашем случае — 1 Гбит) необходимо поделить на ширину внутренней шины данных (x8), таким образом, ее можно записать как «256Mx8» (или, с учетом количества логических банков — «32Mx8x8 банков», хотя такая форма записи встречается намного реже). Емкость физического банка (ранка) вычисляется несколько более сложным образом: емкость микросхемы (в битах) делится на 8 (для пересчета бит в байты), умножается на ширину внешней шины данных и делится на ширину внутренней шины данных. В нашем случае получаем: 1 (Гбит) / 8 (бит/байт) x 64 (бит) / 8 (бит) = 1 ГБ. Наконец, емкость модуля, как обычно, определяется емкостью физического банка (ранков), помноженной на количество физических банков (ранков). Согласно SPD, сассматриваемые модули являются одноранковыми, в связи с чем емкость модуля совпадает с емкостью ранка и соответствует заявленным 1 ГБ.

Принципиальные изменения касаются и представления всех временных параметров (таймингов) микросхем модуля памяти. Вместо использования привычных наносекунд для указания времени цикла (tCK) и всех остальных таймингов (за исключением tCL, о чем позже), в DDR3 SPD все параметры выражены в «единицах MTB». Само значение MTB — Medium Time Base можно было бы перевести как значение «среднего» опорного временного интервала, однако мы предпочли вариант перевода «основной опорный временной интервал». Заметим, что стандартом предусмотрена также возможность использования единиц FTB — Fine Time Base, т.е. «точного» опорного временного интервала (возможно, для более тонкой подстройки каких-либо временных параметров малой длительности, порядка нескольких пикосекунд), однако в настоящей ревизии DDR3 SPD 1.0 оно не используется. Величина MTB (а также FTB) задается в наносекундах рациональным отношением (делимое : делитель), в связи с чем может принимать довольно широкий интервал значений (теоретически — от 255 до 1/255 нс). Стандартом DDR3 SPD по умолчанию утверждено значение MTB, равное 1/8 = 0.125 нс. Другим важным отличием, касающимся временных параметров, является отказ от использования привычных для DDR2 значений времени цикла (tCK), соответствующих основной (CL X), уменьшенной (CL X-1) и дважды уменьшенной (CL X-2) величинам задержки CAS#, выраженных в целых тактах шины памяти. Вместо этого, в DDR3 SPD представлены единственные значения времени цикла (tCKmin) и задержки CAS# (tAAmin), выраженные в единицах MTB (которые можно перевести в наносекунды). В то же время, заметим, что понятие «поддерживаемых длительностей сигнала CAS#» (выраженных в целых тактах шины памяти) по-прежнему используется в DDR3 SPD, в связи с чем можно получить значения времени цикла, соответствующие тем или иным значениям tCL, т.е. провести аналогию с данными DDR2 SPD. В нашем случае tCKmin = 1.5 нс, tAAmin = 13.5 нс (9 тактов), а поддерижваемые значения CAS# — 9, 8 и 6. Основываясь на этих данных, можно представить следующие допустимые значения времени цикла (частоты шины памяти) и схем таймингов:

| Задержка CAS#, тактов | 9 | 8 | 6 |

|---|---|---|---|

| Время цикла (tCK), нс | 1.5 | 1.6875 | 2.25 |

| Частота шины памяти, МГц (скоростная категория DDR3) | 666.7 (DDR3-1333) | 592.6 (DDR3-1185) | 444.4 (DDR3-889) |

| tRCD, тактов | 9 | 8 | 6 |

| tRP, тактов | 9 | 8 | 6 |

| tRAS, тактов | 24 | 21.3 | 16 |

Конечно, представленные схемы таймингов, соответствующие условным скоростным категориям «DDR3-1185» и «DDR3-889» представляют скорее теоретический, нежели практический интерес. Мы приводим их исключительно для того, чтобы провести аналогию между содержимым SPD модулей памяти типа DDR2 и DDR3. На наш взгляд, значение «поддерживаемых длительностей CAS#» следовало бы вообще исключить, оставив при этом единственное значение минимальной задержки CAS# (tAAmin), соответствующей максимальной частоте шины памяти (минимальному времени цикла, tCKmin).

Наконец, несколько по-иному представляется идентификационная информация кода производителя модулей памяти по JEDEC. Вместо представления полного 8-байтного кода с «честным» указанием последовательности одинаковых кодов продолжения (7Fh, количество которых может достигать 7), используется элегантный подход с указанием количества кодов продолжения (в нашем случае — 2) и кода производителя (9Eh), требующий всего 2 байта данных. Стандартом DDR3 SPD предусмотрено также указание кода производителя микросхем модуля (впервые для SPD модулей памяти категорий DDR), однако в нашем случае производитель не пожелал воспользоваться предоставленной возможностью. Дата изготовления модуля, его серийный номер и Part Number указываются аналогично, из них в рассматриваемых модулях присутствует только последний («CM3X1024-1800C7DHX»), причем он несколько не соответствует указанному на этикетке («CM3X1024-1800C7DIN»).

Поскольку изучаемые модули поддерживают расширения XMP, рассмотрим также содержимое «нестандартной» части SPD, соответствующей профилям XMP и представленной байтами 176-254.

Описание стандарта XMP:

Intel(R) Extreme Memory Profile (XMP) Specification: Enthusiast Extension to the JEDEC DDR3 SPD 1.0 Specification. Rev 1.04, September 2007

| Параметр | Байт(ы) | Значение | Расшифровка |

|---|---|---|---|

| Строка идентификации XMP | 176, 177 | 0Сh, 4Ah | Есть поддержка XMP |

| Организация профилей XMP | 178 | 00h | Профиль №1: отключен (?) Профиль №2: отключен |

| Ревизия XMP | 179 | 10h | Ревизия 1.0 |

| Основной опорный временной интервал (MTB) (делимое : делитель) | 180, 181 | 01h, 09h | 0.111 нс (1 : 9) |

| Профиль №1 | |||

| Уровень питающего напряжения (VDD) | 185 | 40h | 2.00 V |

| Минимальный временной цикл (tCKmin) | 186 | 0Ah | 1.11 нс (900.0 МГц) |

| Минимальная задержка CAS# (tAAmin) | 187 | 46h | 7.77 нс (7 тактов) |

| Поддерживаемые длительности сигнала CAS# (CL) | 188, 189 | 0Ch, 00h | 6, 7 |

| Минимальная задержка записи CAS# (tCWLmin) | 190 | 46h | 7.77 нс (7 тактов) |

| Минимальное время подзарядки данных в строке (tRPmin) | 191 | 46h | 7.77 нс (7 тактов) |

| Минимальная задержка между RAS# и CAS# (tRCDmin) | 192 | 46h | 7.77 нс (7 тактов) |

| Минимальный период восстановления после записи (tWRmin) | 193 | 87h | 15.0 нс (13.5 тактов) |

| Минимальная длительность импульса сигнала RAS# (tRASmin) | 195, 194 | C8h, 10h | 22.22 нс (20.0 тактов) |

| Минимальное время цикла строки (tRCmin) | 196, 194 | 95h, 10h | 45.0 нс (40.5 тактов) |

| Максимальное значение периодического интервала регенерации (tREFImax) | 197, 198 | 46h, 00h | 7.77 мс |

| Минимальное время цикла регенерации (tRFCmin) | 199, 200 | DEh, 03h | 110.0 нс (99 тактов) |

| Минимальная внутренняя задержка между командами READ и PRECHARGE (tRTPmin) | 201 | 44h | 7.55 нс (6.8 тактов) |

| Минимальная задержка между активизацией соседних строк (tRRDmin) | 202 | 36h | 6.0 нс (5.4 такта) |

| Минимальное время задержки Four Activate Window (tFAWmin) | 204, 203 | 0Eh, 01h | 30.0 нс (27 тактов) |

| Минимальная внутренняя задержка между командами WRITE и READ (tWTRmin) | 205 | 44h | 7.55 нс (6.8 тактов) |

| Временные оптимизации обращения команд WRITE-to-READ и READ-to-WRITE | 206 | 00h | W-R: по умолчанию R-W: по умолчанию |

| Временные оптимизации обращения команд BACK-to-BACK | 207 | 00h | По умолчанию |

| Задержка передачи адреса, команд и контрольных сигналов (System CMD Rate) | 208 | 00h | По умолчанию |

Содержимое общей части расширений XMP включает в себя строку идентификации поддержки XMP (присутствует), номер ревизии XMP (1.0), информацию о содержащихся профилях (в содержимом XMP рассматриваемых модулей эта информация отсутствует, т.е. оба профиля оказываются как бы отключенными, хотя на самом деле присутствуют данные первого профиля — возможно, это связано с использованием производителем более ранней ревизии расширений XMP по сравнению с той, которую мы использовали при расшифровке значений), а также величину опорного временного интервала (MTB), которая задается аналогичным образом (отношением 8-битных делимого и делителя). В рассматриваемом случае, для удобства представления всех остальных значений времен, эта величина уменьшена до 1/11 = 0.111 нс.

Далее представлена информация о профилях XMP (первый — в области 185-219 байт, второй — с 220-го по 254-й байт), которые в нашем случае представлены лишь одним (первым) профилем. Содержимое профиля во многом повторяет содержимое стандартной части DDR3 SPD (большинство временных парамтеров). Минимальное время цикла (tCKmin) равно 1.11 нс (частота шины памяти 900 МГц, т.е. режим DDR3-1800), а схема таймингов (tRCD-tCL-tRP-tRAS) может быть представлена как 7-7-7-20, что в точности соответствует характеристикам производителя модулей памяти. Предусмотрена также «уменьшенная» величина задержки CAS# (6), которой мог бы соответствовать временной цикл примерно 1.296 нс (частота примерно 771 МГц, т.е. режим «DDR3-1542») и схема таймингов 6-6-6-17.1, однако, как и в случае стандартного содержимого DDR3 SPD, это не представляет большого практического интереса. Уровень питающего напряжения, указанный в этом профиле XMP, также соответствует рекомендованному значению 2.0 В.Конфигурация тестового стенда

Стенд №1

- Процессор: Intel Core 2 Duo E6850 (2+2 МБ L2, 3.0 ГГц, FSB 333 МГц x 9)

- Чипсет: Intel X38 (штатная частота FSB 333 МГц)

- Материнская плата: ASUS Maximus Extreme, версия BIOS 0403 от 26.10.2007

- Память: 2 x 1 ГБ Corsair TWIN3X2048-1800C7DFIN G в режимах DDR3-1600 и DDR3-1800 (профиль XMP).

- Видео: Sapphire Radeon X1900XTX, 512 МБ

- HDD: Western Digital WD1600, SATA

Исследование подсистемы памяти с участием рассматриваемых модулей проводилось в стандартном (сертифицированном JEDEC) режиме DDR3-1600 с использованием стандартных настроек SPD, и в неофициальном режиме DDR3-1800, достигаемом при использовании профиля XMP. В обоих случаях использовалось рекомендованное производителем питающее напряжение 2.0 В (на 0.5 В выше стандартного) и применялась поставляемая в комплекте модулей фирменная система охлаждения Airflow (без регулировки скорости вращения вентиляторов). При этом в обоих режимах тестирования предпринималась попытка достижения минимально возможной схемы таймингов, не приводящей к сбоям в работе подсистемы памяти.

| Параметр | Стенд №1 | |||

|---|---|---|---|---|

| Частота процессора, МГц (частота FSB x FID) | 3200 (400 x 8) | 3150 (450 x 7) | ||

| Частота памяти, МГц (скоростной режим DDR3) | 800 (DDR3-1600) | 900 (DDR3-1800) | ||

| Тайминги памяти, напряжение | 9-9-9-24, 2.0 В | 6-6-6-11, 2.0 В | 7-7-7-20, 2.0 В | 7-6-6-13, 2.0 В |

| Средняя ПСП на чтение, ГБ/с, 1 ядро | 7.94 | 8.33 | 9.81 | 9.94 |

| Средняя ПСП на запись, ГБ/с, 1 ядро | 2.85 | 3.24 | 3.74 | 3.86 |

| Макс. ПСП на чтение, ГБ/с, 1 ядро | 9.12 | 9.53 | 11.41 | 11.47 |

| Макс. ПСП на запись, ГБ/с, 1 ядро | 7.31 | 7.31 | 8.22 | 8.22 |

| Средняя ПСП на чтение, ГБ/с, 2 ядра | 10.65 | 11.33 | 12.72 | 13.02 |

| Средняя ПСП на запись, ГБ/с, 2 ядра | 3.06 | 3.40 | 3.75 | 3.82 |

| Макс. ПСП на чтение, ГБ/с, 2 ядра | 11.52 | 12.24 | 13.18 | 13.49 |

| Макс. ПСП на запись, ГБ/с, 2 ядра | 7.29 | 7.29 | 8.22 | 8.22 |

| Минимальная латентность псевдослучайного доступа, нс | 26.7 | 25.6 | 21.1 | 21.1 |

| Минимальная латентность случайного доступа*, нс | 66.0 | 59.4 | 51.1 | 49.1 |

| DOOM3 FPS (640x480, low) | 280.1 | 286.4 | 288.5 | 293.2 |

| FarCry FPS (640x480, low) | 441.2 | 451.0 | 463.9 | 463.9 |

*размер блока 32 МБ

В режиме DDR3-1600 в качестве схемы таймингов по умолчанию BIOS материнской платы ASUS Maximus Extreme, участвующей в наших тестах, была выбрана схема 9-9-9-24 (хотя она и относится к скоростному режиму DDR3-1333, указанному в SPD в качестве режима по умолчанию). Частота системной шины чипсета была установлена равной 400 МГц, соответственно, частота процессора составила 3.2 ГГц (400 МГц x 8, что соответствует разгону последнего на 6.7%). Соотношение частот FSB:DRAM составляет 1:2, и данный режим работы подсистемы памяти можно считать синхронным, т.е. характеризующимся минимальными задержками. Заметим также, что в этом режиме теоретическая пропускная способность (ПС) системной шины (12.8 ГБ/с) оказывается вдвое ниже теоретической пропускной способности памяти (ПСП), равной 25.6 ГБ/с. Таким образом, реально достижимые значения ПСП в лучшем случае составят 50% от теоретического скоростного потенциала двухканальной DDR3.

Признаемся честно, на практике мы ожидали получить еще меньшее раскрытие скоростного потенциала DDR3-1600 на этой платформе, поскольку наше недавнее исследование двухканальной DDR2-800 на чипсете Intel X48 (который отличается от участника наших сегодняшних тестов Intel X38 лишь тем, что 400-МГц частота FSB для него является штатной, а не «разгонной») показало, что данная платформа способна раскрыть лишь примерно 70% скоростного потенциала ПС процессорной шины (и ПСП двухканальной DDR2-800). Учитывая, что ПСП двухканальной DDR3-1600 в два раза выше, изначально мы ожидали увидеть реальные значения ПСП, соответствующие не более 35% от теоретического максимума.

Тем не менее, реальные значения ПСП, приведенные в таблице, оказались намного выше, что особенно заметно по максимальной реальной ПСП на чтение при двухпоточном доступе к памяти — она составляет примерно 11.5 ГБ/с, т.е. 90% от теоретической ПС системной шины (соответственно, 45% от теоретической ПСП DDR3-1600). Использование «экстремальной» схемы таймингов (а в этом рассматриваемые модули показали значительный «запас прочности», поскольку она составила значения 6-6-6-11) еще более увеличивает значение максимальной реальной ПСП на чтение. В этом случае, при «двухъядерном» доступе она составляет 12.24 ГБ/с, т.е. свыше 95% от теоретической ПС системной шины. Таким образом, «виновной» в нераскрытии скоростного потенциала подсистемы памяти в нашем предыдущем исследовании оказалась не системная шина, а... сама DDR2-800, точнее — контроллер памяти чипсетов Intel 3 Series, который неспособен достичь 100% утилизацию ПСП в условиях интенсивного доступа (когда поток данных от процессора чипсету равен по своей интенсивности потоку данных от контроллера памяти к оперативной памяти). В нашем же случае, когда поток данных по системной шине (от процессора к чипсету) оказывается вдвое меньшим по сравнению с потоком данных от оперативной памяти к контроллеру памяти (т.е. утилизация ПСП не превышает 50%), контроллер памяти оказывается полностью способным вовремя предоставить необходимые данные.

То же самое можно сказать и о режиме DDR3-1800, в котором частота системной шины была увеличена до 450 МГц (частота процессора при этом составила 450 МГц x 7 = 3.15 ГГц, что соответствует 5%-ному разгону), а частота шины памяти возросла до 900 МГц (соотношение частот FSB:DRAM осталось прежним, 1:2). В этом случае теоретическая ПС системной шины возрастает до 14.4 ГБ/с, а теоретическая ПСП — соответственно, до 28.8 ГБ/с. Максимальная реальная ПСП на чтение в двухпоточном доступе при применении схемы таймингов по умолчанию (7-7-7-20, соответствующей профилю XMP) составляет примерно 13.2 ГБ/с, что соответствует утилизации примерно 92% ПС системной шины. Уменьшение схемы таймингов до минимально возможной 7-6-6-13 увеличивает это значение примерно до 13.5 ГБ/с, т.е. примерно 94% от теоретической ПС FSB.

Важно также отметить, что как применение более скоростной схемы таймингов, так и увеличение частоты FSB и шины памяти приводит к ощутимому снижению задержек при случайном доступе в память. В первом случае, при переходе от «стандартной» схемы таймингов 9-9-9-24 к «экстремальной» 6-6-6-11 снижение латентности случайного доступа составляет 10%. Увеличение частоты FSB и DRAM на 12.5% приводит к более ощутимому снижению задержек — примерно на 23%, если сравнивать значения при «стандартных» схемах таймингов, и примерно на 17% при сравнении значений в «экстремальных» условиях.Итоги

Исследованные модули памяти Corsair DOMINATOR TWIN3X2048-1800C7DFIN G проявили себя в качестве надежных представителей нового поколения памяти DDR3. В максимальном скоростном режиме DDR3-1600, сертифицированном JEDEC, они оказались способными функционировать с максимально низкой схемой таймингов 6-6-6-11 (при рекомендованном питающем напряжении 2.0 В), а в неофициальном режиме DDR3-1800, указанном в профиле XMP, рекомендованную схему таймингов 7-7-7-20 удалось снизить до 7-6-6-13.

Величины реально достижимой пропускной способности памяти в обоих случаях (как DDR3-1600, так и DDR3-1800) составили почти 95% от теоретической ПС системной шины, выступающей в данном случае главным ограничителем скоростного потенциала подсистемы памяти. Иными словами, использование рассматриваемых модулей памяти DDR3 позволяет «выжать максимум» производительности подсистемы памяти на данной платформе (процессоры семейства Intel Core 2, чипсеты Intel 3 Series). Заметим, что такого эффекта не удается достичь при использовании модулей памяти DDR2-800 на этой платформе, несмотря на то, что это должно быть возможно теоретически. Указанное обстоятельство несомненно оправдывает применение более скоростных вариантов модулей памяти (включая DDR3) уже сегодня, на нынешнем поколении платформ Intel.

Средняя текущая цена (количество предложений) в московской рознице:

| Модули памяти Corsair DOMINATOR DDR3-1800 2 x 1ГБ (TWIN3X2048-1800C7DFIN G) | Н/Д(0) |

:no_upscale()/https://cdn.ixbt.site/ixbt-data/j60dmSU4uH/covers/oE39SIaMD9K49PNi3FgOuPM1Sch5fFb5Dj4YiGSC.jpg)

:no_upscale()/https://cdn.ixbt.site/ixbt-data/QCJIvbjT8O/covers/90weYO07imIA2mas0dnMpYk4x9Jw210bvVbnlfQk.jpg)

:no_upscale()/https://cdn.ixbt.site/ixbt-data/8eLrRxMoMm/covers/SEhObdstWSg4I1Vi7vavUUrjuMNrdiPbkeu2XK3B.jpg)